RESEARCH AND DEVELOPMENT METHOD FOR INCREASE NOISE IMMUNITY OF PIPELINE ADC

Экимян А.Р.

Аспирант/Соискатель, Национальный исследовательский университет, МИЭТ г. Москва

ИССЛЕДОВАНИЕ И РАЗРАБОТКА МЕТОДА ПОВЫШЕНИЯ ПОМЕХОУСТОЙЧИВОСТИ КОНВЕЙЕРНОГО АЦП

Аннотация

В данной работе представлен метод повышения помехоустойчивости в конвейерных Аналого-цифровых преобразователей (АЦП) вне зависимости от вариации процесса напряжения и температуры. Так как конвейерный АЦП работает с дифференциальным синхросигналом, то дифференциальный синхросигнал должен быть с 180 фазовым сдвигом, или разница точки пересечения дифференциального сигнала должен быть 0мВ. Если фазовый сдвиг больше или меньше 180, то помехоустойчивость и точность АЦП уменьшится. Так как вся система работает с синхросигналом, то исправления дифференциального синхросигнала является актуальной проблемой. Предлагаемый метод также помогает избежать ошибок времени удержания и установки в триггерах. Предлагаемый метод может использоваться в различных архитектурах конвейерного АЦП.

Ключевые слова: Аналого-цифровой преобразователь, низкочастотный фильтр, фазовый детектор, отношение сигнал/шум, генератор синхросигнала.

Hekimyan A.R.

Postgraduate student, National Research University of Electronic Technology, MIET in Moscow

RESEARCH AND DEVELOPMENT METHOD FOR INCREASE NOISE IMMUNITY OF PIPELINE ADC

Abstract

Differential clock cross point correction method is presented in this paper. The proposed method provides differential clock with minimum crossing error or phase shift is 180 over PVT, which is needed to improve noise immunity of Pipeline ADC. As Pipeline ADC work with differential clock, so crossing error of differential clock could decrease noise immunity. As whole system works with differential clock, correcting phase shift of differential clock is actual issue. Cross point correction method also helps to avoid setup / hold violations in some systems. Proposed architecture can be used in different architecture of Pipeline ADCs.

Keywords: Analog-to-digital Converter (ADC), low pass filter (LPF), phase detector, signal-to-noise ratio (SNR), clock generator.

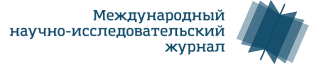

Рис. 1 - 1.5 бит каскад архитектура

На рис. 1 показано 1.5 бит каскад архитектура конвейерного АЦП. Схема работает в двух фазах. Во время первой фазы S1 ключ закрывается и отрицательный вход операционного усилителя соединяется с нулем. S1 и S2 ключи соединяют Cs Cf конденсаторы к входному напряжению, и таким образом конденсаторы заряжаются. Заряд на конденсаторах будет равно входному напряжению. Во те же время аналоговое напряжения подается к компараторам и на выходе компараторов получается цифровой код. Во время второй фазы S1 ключ открывается, S2 ключ соединяет выход аналогового мультиплексора к Cs конденсатору, S3 ключ соединяет Cf конденсатор с выходом операционного усилителя, тем самым операционный усилитель будет работать в режиме отрицательной обратной связи. Аналоговый мультиплексор находит ошибку квантования и подает на вход операционного усилителя. Выход операционного усилителя подается к следующему каскаду конвейерного АЦП. Для 1.5 бит каскад архитектуры коэффициент усиления операционного усилителя равен 2. Это можно получить, если конденсаторы идентичны (Cf = Cs). Если конденсаторы не равны друг другу, то выход напряжение на выходе операционного усилителя будет неправильным. Выход операционного усилителя подается на следующий каскад, который имеет ту же архитектуру.

Все переходные процессы контролируются с помощью дифференциального синхросигнала. Все каскады работают синхронно. Если дифференциальный синхросигнал имеет погрешность, то каскады больше синхронно не будут работать и незначительные помехи будут сильно влиять на схему, так как каскады не синхронно переключаются.

Для нормальной работы конвейерный АЦП [1, С. 113] требуется дифференциальный синхросигнал. Фазовый сдвиг дифференциального синхросигнала приводит к уменьшению помехоустойчивости АЦП и даже может привести сбой системы [2, С. 16]. Фазовый сдвиг дифференциального синхросигнала нельзя игнорировать и исправление фазового сдвига является актуальной проблемой.

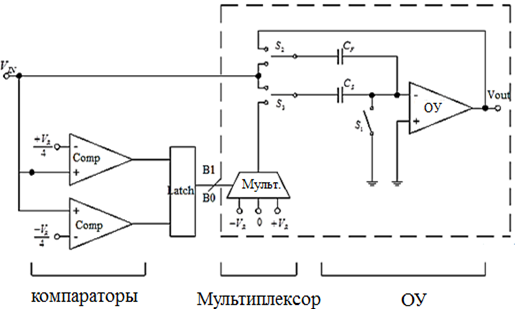

Рис. 2 – (а) Идеальный дифференциальный синхросигнал (б) Неидеальный дифференциальный синхросигнал

На рис.2 показано идеальный дифференциальный синхросигнал и не идеальный дифференциальный синхросигнал [3, С. 310]. Если на вход АЦП подать синхросигнал на рис.1 б, то не только помехоустойчивость уменьшится, еще возможно потеря информации, так как схемы выпорки и хранения в каскадах конвейерного АЦП не будут синхронно делать дискретизацию аналогового сигнала [4, С. 467]. Из-за фазового сдвига дифференциального синхросигнала помехоустойчивость всей системы уменьшится. По этому, исправления дифференциального синхросигнала является актуальной проблемой.

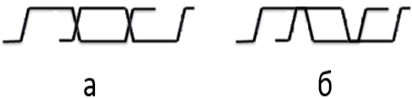

Блок схема исправления [5, С. 2428] дифференциального синхросигнала состоит из фазового детектора (Рис.3), низкочастотного фильтра, дифференциального усилителя и генератора синхросигнала. Выход генератора синхросигнала будет почти идеальный дифференциальный синхросигнал с минимальным фазовым сдвигом, который используется для нормальной работы конвейерного АЦП. Неидеальный дифференциальный синхросигнал подается на входы фазового детектора и одновременно генератора синхросигнала. Выходы генератора синхросигнала подается на конвейерный АЦП.

Рис. 3 – блок-схема исправления дифференциального сигнала

Дифференциальный синхросигнал с фазовым сдвигом подается к входу фазового детектора (Рис. 4).

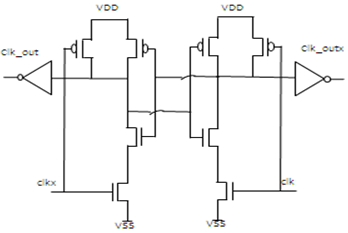

Рис. 4 – Фазовый детектор

Фазовый детектор имеет два выхода. На выходах фазового детектора будут импульсы, которые равны по длине фазовому сдвигу на входах. Тем самым на выходе фазового детектора будет информация фазового сдвига. Выходы фазового детектора подаются на низкочастотный фильтр, который интегрирует сигнал на входе. Низкочастотный фильтр генерирует напряжение, которое соответствует фазовому сдвигу дифференциального синхросигнала. Аналоговое напряжение подается на вход дифференциального усилителя (рис. 4). Необходимо помехоустойчивый дифференциальный усилитель, что бы обеспечить интегрированное напряжения на выходах в зависимости от входов. Для этого необходимо, что бы дифференциальный усилитель имел широкий канал. Это реализовано с помощью последовательных ПМОП транзисторов. Дифференциальный усилитель должен хорошо сбалансирован, так как выходы являются контрольными входами генератора синхросигнала (рис. 6 а.).

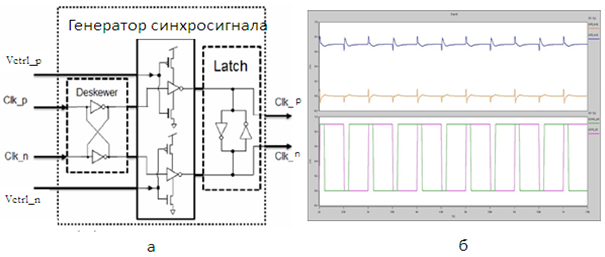

Генератор синхросигнала имеет 4 входа. На два входа подается дифференциальный синхросигнал, остальные два входа для контроля исправления фазового сдвига. Эти входы контролируются с помощи дифференциального усилителя. На рис.6 б. показано входные сигналы генератора синхросигнала.

Рис. 5 – Дифференциальный усилитель

Выходы дифференциального усилителя контролируют фазовый сдвиг, что бы получить на выходе идеальный дифференциальный сигнал. Выходы дифференциального усилителя уменьшают или увеличивают коэффициент заполнения сигнала. Выходной каскад генератора синхросигнала исправляет фазовый сдвиг дифференциального синхросигнала. Дифференциальный выход генератора синхросигнала уже можно использовать для высокоскоростных АЦП.

Рис. 6 – (а) схема генератора синхросигнала, (б) сигналы на входах

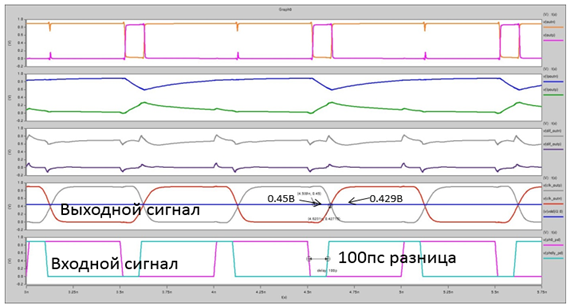

Моделирование схемы было сделано с помощью Hspice [6 С. 196] симулятора. Спроектирован конвейерный АЦП для 16нм FinFet технологии. Были учтены особенности FinFet технологии. Схема смоделировано с вариации процесса, напряжения и температуры. Разница точки пересечения дифференциального сигнала 22мВ, в SS процессе с минимальным напряжением, когда на входе разница точки пересечения 100пс. Частота входного сигнала 1000МГц. Это максимальная частота конвейерного АЦП. Как показано на рис. 6 с разницей 100пс выходной дифференциальный сигнал получается почти идеальным. Предложенный метод не добавляет фазового дрожания синхросигнала. Так как, на выходе используется генератор синхросигнала, который контролируется с помощью дифференциального усилителя, фазовое дрожания синхросигнала не увеличивается.

Рис. 7 – Результаты моделирования

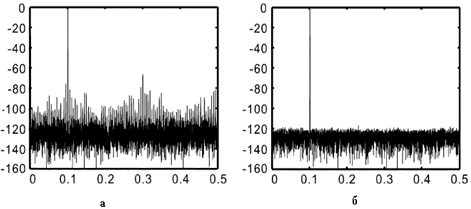

На Рис. 8 а) результаты моделирования без исправления дифференциального сигнала, а на рис. 7 б) с исправлением дифференциального сигнала. Доказано (Рис. 7), что после исправления дифференциального сигнала, отношение сигнал-шум-плюс-искажение (SNDR) улучшается с 62 дБ до 94 дБ, динамический диапазон, свободный от паразитных составляющих (SFDR) улучшается с 70 дБ до 120 дБ. Тем самым увеличивается помехоустойчивость АЦП более 30%.

Рис. 8 – Результат помехоустойчивости АЦП

Схема исправления дифференциального синхросигнала была спроектирована для исправления фазового сдвига синхросигнала в конвейерных АЦП. Результаты моделирования показали, что схема аффективно исправляет фазовый сдвиг. На выходе схемы разница точки пересечения дифференциального синхросигнала получается менее 22мВ, что для Конвейерного АЦП является незначительным, так как максимальная частота конвейерного АЦП 1000МГц. Помехоустойчивость конвейерного АЦП увеличивается более 30%, что дает возможность обработать аналоговый сигнал и преобразовать эго в цифровой сигнал без ошибок.

Предлагаемая схема увеличивает площадь АЦП 7-8%, что приемлемо. Мощность конвейерного АЦП с использованием перемогаемого метода увеличивается 14% (с 14мВт 16мВт). Так как в интегральной схеме используется один АЦП, то 14% увеличение мощности приемлемо.

Список литературы / References

- Экимян А. Р. Повышение помехоустойчивости аналого-цифровых преобразователей конвейерного типа / А. Р. Экимян // Микроэлектроника и информатика –2015. – М.: МИЭТ, 2015. – C. 113.

- Экимян А. Р. Метод исправления дифференциального синхросигнала в конвейерных АЦП / А. Р. Экимян // Потенциал Современной Науки – 2016 — № 8 – С. 16 – 20.

- Hekimyan A. High Accuracy Pipelined ADC Design for Wireless LANs / A. Hekimyan, D. Bulakh, A. Sahakyan // 2015 Internet Technologies and Applications (ITA), September — 2015 — Glyndwr University, Wrexham, Wales, UK. – P. 310 – 313.

- Razavi B. Design of Analog CMOS Integrated Circuits / B. Razavi – New York, NY, USA, 2001 – P. 465 – 471.

- McNeill J. Architecture for Deterministic Digital Background Calibration of a 16- bit 1-MS/s ADC / J. McNeill, M. Coln, B. Larivee // IEEE J. Solid-State Circuits. – 2005. – № 12. – P. 2437 – 2445.

- Hspice Руководство по применению, Синопсис, 2010. – C. 196.

Список литературы на английском языке / References in English

- Hekimyan A. R. Povishenie pomehoustoychovosti analogo-cifrovikh preobrazowateley konveyernogo tipa [Increase noise immunity in pipeline ADCs] / A.R. Hekimyan // Mikroelektronika I informatika [Microelectronics and Nanoelectronics] – M.: MIET 2015 – P. 113. [in Russian]

- Hekimyan A. R. Metod ispravlenija differencial'nogo sinhrosignala v konvejernyh ACP [Method of correcting differential clock in pipeline ADC] / A. R. Hekimyan // Potencial Sovremennoj Nauki [Potential Modern Science]. – 2016 – № 8 – P. 16-20. [in Russian]

- Hekimyan A. High Accuracy Pipelined ADC Design for Wireless LANs / A. Hekimyan, D. Bulakh, A. Sahakyan // 2015 Internet Technologies and Applications (ITA), September — 2015 — Glyndwr University, Wrexham, Wales, UK. – P. 310 – 313.

- Razavi B. Design of Analog CMOS Integrated Circuits / B. Razavi — New York, NY, USA. –2001. – P. 465 – 471.

- McNeill J. Architecture for Deterministic Digital Background Calibration of a 16- bit 1-MS/s ADC / J. McNeill, M. Coln, B. Larivee // IEEE J. Solid-State Circuits. – 2005. – № 12. – P. 2437 – 2445.

- Hspice Rukovodstvo po primeneniju [Application Manual] Synopsys Inc. – 2010. 196 p. [in Russian]