Оценка качества случайных двоичных последовательностей с применением программируемой логической интегральной схемы

Оценка качества случайных двоичных последовательностей с применением программируемой логической интегральной схемы

Аннотация

В данной статье рассматривается разработка и реализация устройства для оценки качества случайных двоичных последовательностей на базе программируемых логических интегральных схем (ПЛИС). Устройство предназначено для тестирования и проверки аппаратных генераторов случайных последовательностей, что играет критическую роль в обеспечении безопасности и точности в вычислениях в областях, где это особенно важно, таких как криптография и информационная безопасность. В статье подробно описывается процесс выбора аппаратной платформы, разработка методик и алгоритмов оценки, а также конечная реализация устройства с использованием отладочной платы Xilinx Spartan-6. Основное внимание уделено возможностям устройства проводить оценки в реальном времени, высокой точности результатов и экономичности использования ресурсов кристалла ПЛИС. Результаты тестирований подтвердили эффективность разработанной системы и её пригодность для использования в образовательных целях для демонстрации ключевых принципов криптографии и информационной безопасности.

1. Введение

В наше время случайные двоичные последовательности применяются в решении множества задач в математике, технике и криптографии. Они играют критическую роль в обеспечении безопасности и точности вычислений. Важным инструментом в этой области является устройство для оценки двоичных последовательностей на базе программируемых логических интегральных схем, предназначенное для тестирования и проверки аппаратных генераторов случайных последовательностей , . Такое устройство позволяет оценивать качество генерирования последовательностей с высокой степенью точности и эффективности.

Основная цель данной работы – разработать и реализовать на ПЛИС блок оценки качества случайных двоичных последовательностей с использованием вероятностного подхода . Реализация такого блока актуальна, так как позволяет гибко и эффективно тестировать аппаратные генераторы случайных последовательностей в режиме реального времени. Для достижения этой цели необходимо решить следующие задачи:

- изучить существующие методы оценки генераторов двоичных последовательностей на основе вероятности;

- выбрать подходящую аппаратную платформу для реализации устройства;

- разработать принципы функционирования и интерфейс взаимодействия с пользователем;

- спроектировать и реализовать блоки вычисления вероятности, управления параметрами, отображения на светодиодах, генерации случайных чисел;

- создать и настроить специализированный микроконтроллер, написать для него программное обеспечение;

- провести тестирование устройства и оценить его аппаратные затраты.

Применение данной разработки имеет значительный потенциал в образовательной сфере, где она может быть использована для создания лабораторных работ и курсов по криптографии и информационной безопасности. Описание функциональности устройства также может служить основой для практических занятий.

Техническая реализация устройства включает использование IP-ядра делителя для точного вычисления отношения количества единиц к общей длине двоичной последовательности. Это ядро позволяет пользователю задавать параметры деления и выбирать формат вывода результатов, что является ключевой особенностью системы.

Разработка такого устройства на отладочной плате Xilinx Spartan-6 LX9 MicroBoard , , использующей Vivado Design Suite для проектирования и отладки, обеспечивает доступ к необходимым ресурсам и интерфейсам для успешной реализации проекта.

2. Проектирование аппаратного блока

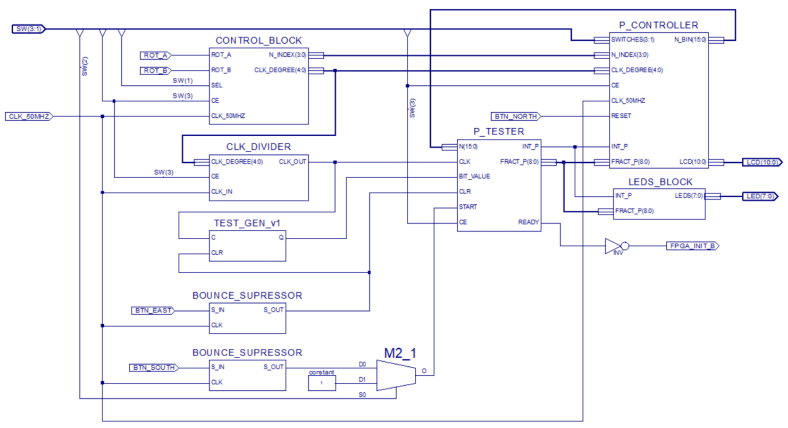

Устройство состоит из четырех блоков: генераторы последовательностей, вычисление вероятности, управление параметрами и контроллер с памятью. Пользователь выбирает тип генератора и задает длину выборки и частоту. Последовательность бит подается на блок подсчета статистики, который вычисляет вероятность получения единиц в последовательности. Эти данные отображаются на светодиодах и дисплее. Устройство имеет удобный интерфейс для взаимодействия с пользователем. Управление осуществляется с помощью переключателей и кнопок, а результаты отображаются на дисплее. Устройство работает в ручном и автоматическом режиме. Параметры и результаты отображаются на жидкокристаллическом дисплее.

Блок управления параметрами позволяет пользователю выбирать частоту синхронизации F и длину выборки N. Для каждого значения частоты и размера выборки представлены соответствующие двоичные коды. Таким образом, пользователь может указать нужные значения F и N, используя соответствующие двоичные комбинации.

Модуль предназначен для обработки случайных последовательностей длиной от 32 до 65535 бит. Интерфейс блока вычисления вероятности состоит из четырех входных и двух выходных портов. Входы включают в себя информацию о размере выборки, тактовую частоту, двоичную последовательность, сигнал очистки и сигнал запуска процесса оценки. Выходы предоставляют информацию о целой и дробной частях вероятности, а также сигнал о завершении вычислений. Функциональная схема модуля состоит из трех компонентов: блока для вычисления статистики единиц в последовательности, делителя и шинного мультиплексора. Дополнительное описание каждого компонента предоставлено в следующих разделах. Устройство STAT_BLOCK имеет те же входы, что и P_TESTER.

Оно предоставляет информацию о количестве единиц в последовательности, длине выборки и завершении вычислений через порты "n1(15:0)", "N_fix(15:0)" и "READY". Функциональная схема блока состоит из счетчиков, компаратора и регистров. Схема включает в себя два режима работы: ручной и автоматический. В ручном режиме корректность работы компонентов системы проверена. В автоматическом режиме статистика накапливается непрерывно за счет постоянного сигнала START, при этом длина выборки составляет 6.

В ходе выполнения работы были проведены следующие этапы схемотехнического проектирования: разработка IP-ядра делителя, проектирование шинного мультиплексора, создание генераторов двоичных, тестовых, псевдослучайных и истинно-случайных последовательностей, разработка блока управления параметрами, блока делителя частоты, блока отображения данных на светодиоды, а также проектирование периферийного микроконтроллера. Эти этапы позволяют создать и управлять сложной цифровой системой, обеспечивая необходимую функциональность и надежность ее работы. Комплексный подход к проектированию данных блоков способствует эффективной реализации цифровых устройств и систем, обеспечивая оптимальное соотношение между функциональностью, производительностью и ресурсами системы.

Рисунок 1 - Архитектура аппаратного блока

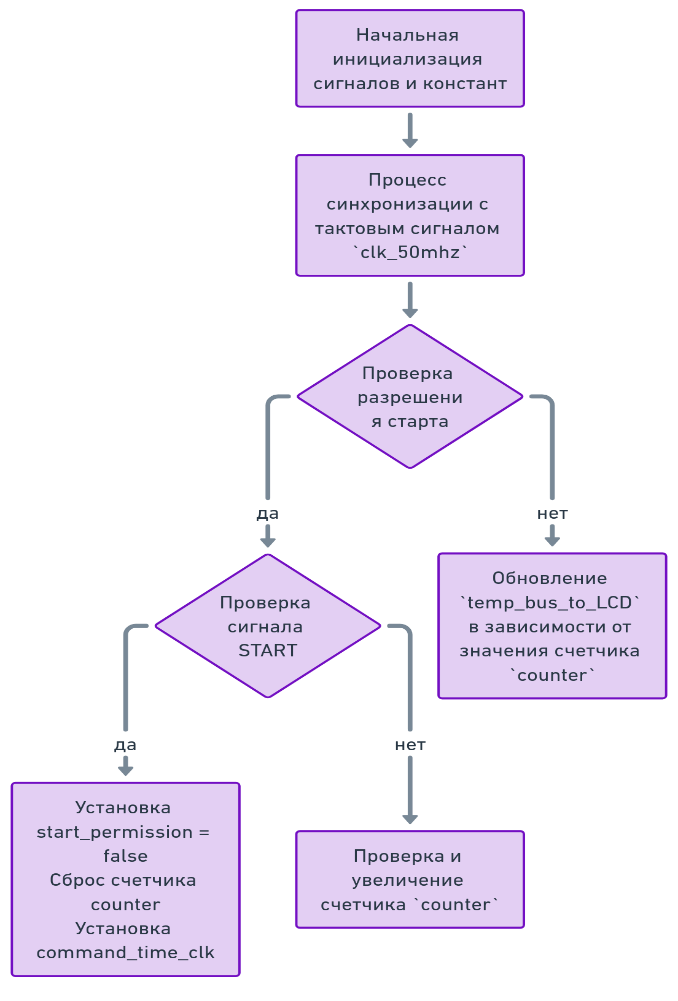

3. Разработка программной части

При выполнении программной части в двоичном коде необходимо выбрать подходящую систему команд для процессора. В проекте были выбраны 18 команд, где каждая команда имеет свой уникальный шестиразрядный код CODE(5:0) и двенадцатиразрядное поле данных Data(11:0).

Таблицы подстановок, хранящиеся в памяти ROM_1024х18, являются важной частью работы и выполняют различные преобразования с данными. При выполнении программы или подпрограммы, устройство может обращаться к этим таблицам для выполнения соответствующих операций на основе заданных значений в таблицах. В проекте имеются следующие таблицы подстановок:

1. Таблица подстановки для двоично-десятичного кода вероятности. Используется в процессе преобразования двоичной дробной части вероятности в эквивалентный двоично-десятичный код. Она расположена во второй половине памяти ROM_1024x18, начиная с адреса 512 и заканчивая адресом 10.

2. Таблица подстановки для двоично-десятичного кода погрешности (см. табл.).

Таблица 1 - Подстановки для двоично-десятичного кода погрешности

DEC | B3 | B2 | B1 | B0 | N | Коэф. Стьюд. t | Погрешность выборки, DEC | Погрешность перевода, DEC | Суммарная погрешн., DEC |

4 | 0 | 1 | 0 | 0 | 32 | 2,02 | 0,178544 | 0,000977 | 0,1795 |

5 | 0 | 1 | 0 | 1 | 64 | 1,96 | 0,1225 | 0,000977 | 0,1235 |

6 | 0 | 1 | 0 | 1 | 128 | 1,96 | 0,086621 | 0,000977 | 0,0876 |

7 | 0 | 1 | 0 | 1 | 256 | 1,96 | 0,06125 | 0,000977 | 0,0622 |

8 | 1 | 0 | 0 | 1 | 512 | 1,96 | 0,04331 | 0,000977 | 0,.0443 |

9 | 1 | 0 | 0 | 1 | 1024 | 1,96 | 0,030625 | 0,000977 | 0,0316 |

10 | 1 | 0 | 0 | 1 | 2048 | 1,96 | 0,021655 | 0,000977 | 0,0226 |

11 | 1 | 0 | 0 | 1 | 4096 | 1,96 | 0,015313 | 0,000977 | 0,0163 |

12 | 1 | 1 | 1 | 0 | 8192 | 1,96 | 0,010827 | 0,000977 | 0,0118 |

13 | 1 | 1 | 1 | 0 | 16384 | 1,96 | 0,007656 | 0,000977 | 0,0086 |

14 | 1 | 1 | 1 | 0 | 32768 | 1,96 | 0,005414 | 0,000977 | 0,0064 |

15 | 1 | 1 | 1 | 0 | 65535 | 1,96 | 0,003824 | 0,000977 | 0,0048 |

Рисунок 2 - Диаграмма программы компонента COMMANDER

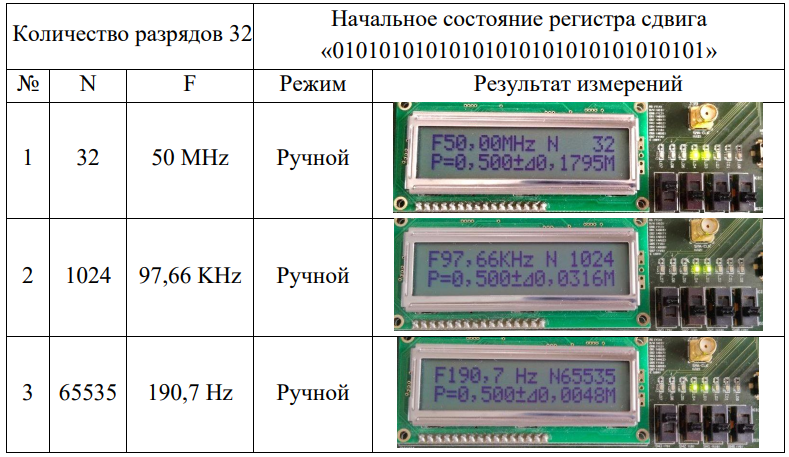

4. Тестирование

Рисунок 3 - Тестирования генератора TEST_GEN_v1

Рисунок 4 - Тестирования генератора TEST_GEN_v1

Рисунок 5 - Тестирование генератора TEST_GEN_v2

По полученным оценкам аппаратных затрат ресурсов кристалла ПЛИС на реализацию блока оценки качества случайных двоичных последовательностей можно сделать вывод о затратах основных аппаратных ресурсов кристалла ПЛИС (триггеров, таблиц преобразования LUT, секций КЛБ) менее 11%, что свидетельствует об экономичности разработанной схемы устройства и хорошем качестве проектирования. В оценку аппаратных затрат блока оценка качества случайных двоичных последовательностей не вошёл периферийный контроллер, задача которого заключается в реализации интерфейса взаимодействия с пользователем. Блок P_TESTER предоставляет гибкость при работе с выборками, так как он способен обрабатывать последовательности с фиксированной длиной выборки, а также с переменной длиной, что позволяет адаптировать его к различным аппаратным решениям.

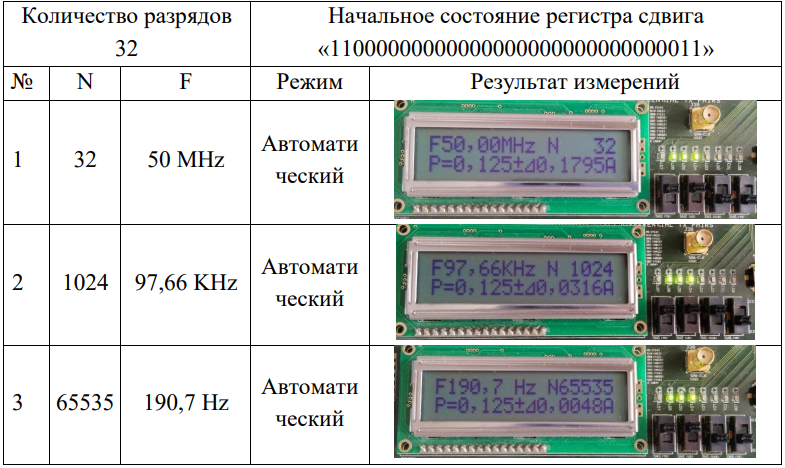

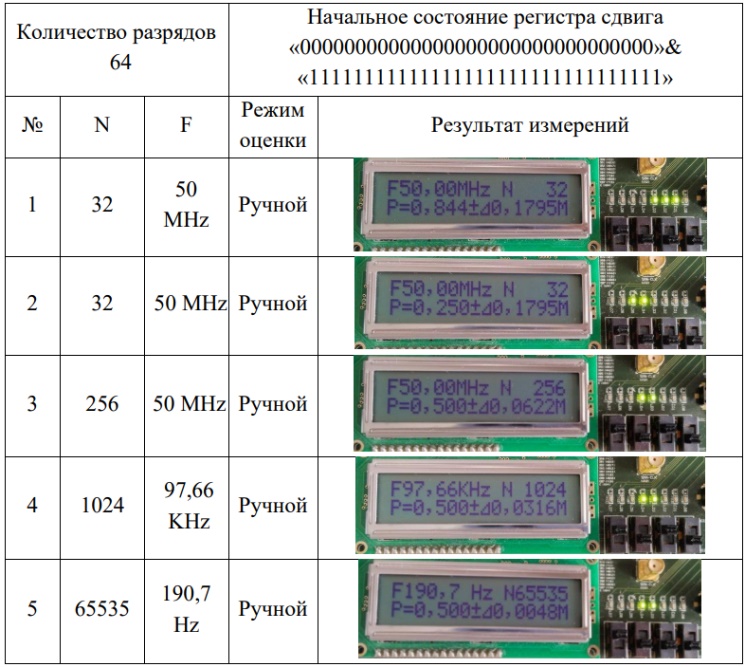

В работе также были проведены эксперименты с использованием генераторов Фибоначчи и Галуа для создания псевдослучайных двоичных последовательностей. Целью было изучение свойств и сравнение качества генерируемых последовательностей при различных параметрах, таких как частота и длина выборки. Результаты показали, что генератор Фибоначчи имеет постоянную вероятность появления единиц из-за фиксированного периода, в то время как генератор Галуа обладает более высокой степенью случайности. При увеличении длины выборки к периоду генератора можно ожидать стабильные результаты. Однако дальнейшее увеличение длины выборки может не привести к значительным изменениям, так как генератор достигнет всевозможных состояний.

Также для проведения экспериментов были выбраны генераторы, основанные на цифровых элементах задержки. Эти генераторы имеют различное количество цифровых элементов задержки, такие как 1, 3, 5 и 7. Вероятность появления единиц в последовательностях генераторов на различном количестве элементов задержки может изменяться в зависимости от частоты и длины выборки. Разброс значений вероятности, выраженный через доверительные интервалы, уменьшается с увеличением длины выборки.

5. Заключение

В данной статье мы рассмотрели разработку и реализацию устройства для оценки качества случайных двоичных последовательностей на базе программируемых логических интегральных схем. Это устройство предоставляет возможность проведения точных и эффективных испытаний аппаратных генераторов случайных последовательностей, что крайне важно для обеспечения безопасности и точности в высокотехнологичных областях, таких как криптография и информационная безопасность.

Проект включал несколько ключевых этапов: от выбора аппаратной платформы и разработки алгоритмов до создания и тестирования готового устройства. Результаты тестирования подтвердили высокую эффективность разработанного блока оценки качества, что позволяет оценить генерируемые последовательности в реальном времени с высокой точностью.

Особое внимание было уделено удобству использования разработанного устройства, включая интуитивно понятный интерфейс и возможность работы в ручном и автоматическом режимах. Экономичность использования ресурсов кристалла ПЛИС и функциональность системы, позволяющая обрабатывать как фиксированную, так и переменную длину последовательностей, делают эту разработку пригодной не только для лабораторных исследований, но и для образовательных целей в курсах по криптографии и информационной безопасности , .

В заключение, данная разработка демонстрирует важность комплексного подхода к проектированию и реализации аппаратных систем, которые требуют высокой степени надежности и точности. Благодаря успешной реализации проекта и его потенциалу в образовательной сфере, ожидается, что устройство найдет широкое применение как в научных, так и в образовательных учреждениях, способствуя повышению качества обучения и исследований в области информационной безопасности.