МОДЕЛИРОВАНИЕ ТУННЕЛЬНОГО ТОКА В ЭЛЕМЕНТАХ ФЛЕШ-ПАМЯТИ

Жевняк О.Г.

кандидат физико-математических наук, доцент, Белорусский государственный университет

МОДЕЛИРОВАНИЕ ТУННЕЛЬНОГО ТОКА В ЭЛЕМЕНТАХ ФЛЕШ-ПАМЯТИ

Аннотация

В настоящей статье осуществлено моделирование туннельного тока в МОП-транзисторах, являющихся основой элементов флеш-памяти. C его помощью было исследовано влияние затворного и стокового напряжения, а также толщины туннельного окисла МОП-транзистора на распределение плотности туннельного тока вдоль проводящего канала транзистора.

Ключевые слова: Элемент флеш-памяти, туннелирование электронов, МОП-транзистор, туннельный ток.

Zhevnyak О.G.

PhD in physics and mathematics, associate professor, Belarussian State University

SIMULATION OF TUNNELING CURRENT IN FLASH-MEMORY CELLS

Abstract

In present paper the simulation of tunneling current in MOS-transistors is fulfilled. The flash-memory cells are constructed on the base of these transistors. By using simulation results the effects of gate and drain voltage as well as tunnel oxide thickness on tunnel current along the transistors channel are studied.

Keywords: Flash-memory cell, electron tunneling, MOS-transistor, tunneling current.

Современная жизнь практически немыслима без использования флеш-памяти. Основным элементом этой памяти является субмикронный МОП-транзистор, имеющий встроенный внутри подзатворного окисла дополнительный электрод, накапливающий заряды (см., например, [1–2]). Разработка надежных и быстродействующих элементов флеш-памяти, а, следовательно, и МОП-транзисторов требует глубокого знания туннельных процессов, протекающих в этих транзисторах между проводящим каналом и встроенным электродом через пленку оксида. Основные трудности в численном изучении этих процессов связаны с тем, что форма потенциальных барьеров, образуемых оксидными пленками, имеет сложную форму и непостоянна вдоль канала по направлению от истока к стоку [2 – 5]. Ситуация также осложняется тем, что направление дрейфового тока в МОП-транзисторе также непостоянно вдоль канала и зависит как от конструктивно-технологических параметров прибора, так и от приложенных к его электродам напряжений. В этой связи наиболее эффективным и точным методом исследования процесса туннелирования электронов в современных транзисторных структурах является численное моделирование [4; 6; 7].

В настоящей работе на основе кинетического моделирования осуществлен расчет плотности туннельного тока в отношении к плотности дрейфового тока вдоль проводящего канала МОП-транзистора. Будет рассматриваться МОП-ячейка флеш-памяти, у которой встроенный электрод отделен от проводящего канала МОП-транзистора туннельным оксидом толщиной от 2 до 4 нм.

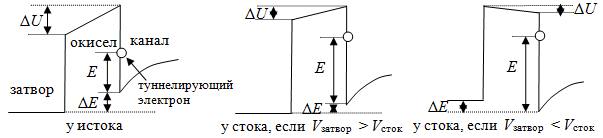

На рис. 1 представлены схематически энергетические диаграммы, поясняющие особенности процесса туннелирования электронов через исследуемую структуру. Главная из них заключается в том, что энергия электронов Е, падение напряжения в окисле кремния ΔU и сдвиг энергетических уровней ΔE могут очень существенно изменяться вдоль проводящего канала, от истока к стоку. Причинами изменения величин ΔU, ΔE и E вдоль канала являются, с одной стороны, разогрев электронов при их дрейфе в канале, а, с другой стороны, сложная зависимость величины электрического потенциала от координаты вдоль канала в субмикронных МОП-транзисторах, обусловленная скрещиванием полей, создаваемых отдельно стоковым и затворным напряжениями. В этой связи рассчитать плотность туннельного тока, которая зависит от указанных величин ΔU, ΔE и E, можно только определив их в каждой точке канала у поверхности Si/SiO2 с помощью численного моделирования электронного переноса вдоль канала. Данное моделирование позволяет адекватно рассчитать изменение энергии электронов вдоль канала, учесть влияние затворного и стокового напряжений на ход электрического потенциала у границы Si/SiO2 и рассчитать изменение величин ΔU и ΔE вдоль канала. Алгоритм данного моделирования описан в нашей работе [7].

Рис. 1 - Энергетические диаграммы потенциального барьера, формируемого подзатворным окислом и приложенными к затвору и стоку прибора напряжениями у встроенного электрода.

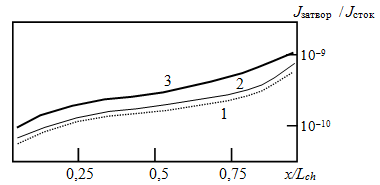

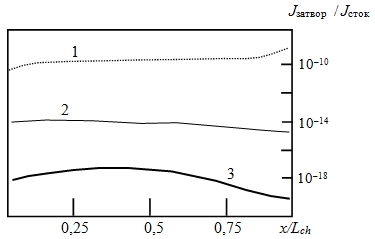

На рис. 2 – 4 представлены полученные при проведении численного моделирования распределения относительных значений плотности туннельного тока вдоль проводящего канала исследуемого МОП-транзистора. Рассматривался прибор с длиной проводящего канала 0,4 мкм, толщиной подзатворного окисла 5,6 нм, концентрацией акцепторной примеси 1024 м–3 и глубиной залегания стоковой области 10–7 м.

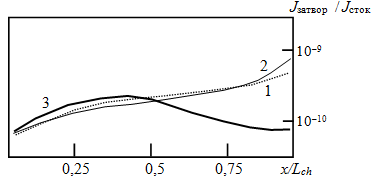

Рис. 2 - Отношение плотностей туннельного тока и тока в проводящем канале вдоль его длины для разных значений затворного напряжения: 1 – Vзатвор = 1 В; 2 – Vзатвор = 2 В; 3 – Vзатвор = 1 В; Vсток = 2 В; dтун = 2 нм.

Рис. 3 - Отношение плотностей туннельного тока и тока в проводящем канале вдоль его длины для разных значений толщины туннельного окисла: 1 – dтун = 2 нм; 2 – dтун = 3 нм; 3 – dтун = 4 нм; Vзатвор = 2 В; Vсток = 2 В.

Как показывают полученные зависимости, наибольшее влияние на величину туннельного тока, как и следовало ожидать, оказывает толщина туннельного оксида. С увеличением этой толщины на 1 нм величина туннельного тока уменьшается в среднем на 4 порядка величины.

Рис. 4 - Отношение плотностей туннельного тока и тока в проводящем канале вдоль его длины для разных значений стокового напряжения: 1 – Vсток = 1 В; 2 – Vсток = 2 В; 3 – Vсток = 3 В; Vзатвор = 2 В; dтун = 2 нм.

Заметное, хотя и не столь существенное, влияние оказывает и затворное напряжение. С его увеличением туннельный ток растет, что обусловлено увеличением падения напряжения на подзатворном окисле, что приводит к увеличению величины среза вершины потенциального барьера и усилением процесса туннелирования в результате заметного уменьшение высоты барьера.

Полученные результаты показывают, что влияние стокового напряжения является довольно специфическим, что проявляется то в увеличении, то в уменьшении туннельного тока при определенных соотношениях между величинами затворного и стокового напряжений. Увеличение стокового напряжения приводит к росту энергии электронов в проводящем канале МОП-транзистора, что увеличивает интенсивность туннелирования электронов через туннельный оксид. Однако с ростом стокового напряжения значительно усиливается его влияние на изменение электрического потенциала у поверхности раздела Si/SiO2, что не может не изменять определенным образом величину ΔU и таким образом влиять на процесс туннелирования. Причем при определенных условиях может наблюдаться как усилении, так и ослабление процесса туннелирования. Последнее явление возможно связано с уводом электронов вблизи стока в глубь подложки и значительным уменьшением их концентрации у поверхности раздела Si/SiO2.

Таким образом, в настоящей статье с помощью кинетического моделирования электронного переноса в канале кремниевого МОП-транзистора исследовано влияние затворного и стокового напряжения, а также толщины туннельного окисла на распределение плотности туннельного тока через пленку туннельного оксида вдоль проводящего канала транзистора. Показано определяющее влияние затворного напряжения и толщины туннельного окисла на величину плотности туннельного тока, а также установлено противоречивое влияние стокового напряжения на эту величину.

Литература

- Majkusiak B. Gate tunnel current in an MOS-transistor // IEEE Trans. Electron. Dev. 1990. Vol. 34, No 4. P. 1087–1092.

- Ranuarez J. C., Deen M. J., Chen C.-H. A review of gate tunneling in MOS devices // Microelectronics Reliability. 2006. Vol. 46, No 12. P. 1939–1956.

- Büttiker M., Landauer R. Transversal time for tunneling // Phys. Rev. Lett. 1982. Vol. 49, No 23. P. 1739–1742.

- Krasnikov G. Ya., Zaitsev N. A., Matyushkin I.V. Tunneling in MOS systems: The dependence of the effective barrier height on the structure of the transition layer at the Si/SiO2 interface in the presence of impurities // Russian Microelectronics. 2001. Vol. 30, No 5. P. 317–323.

- Baik S. J., Choi S., Chung U-In, and Moon J. T. Engineering on tunnel barrier and dot surface in Si nanocrystal memories // Solid-State Electron. 2004. Vol. 48. P. 1475–1481.

- Schenk A., Heiser G. Modeling and simulation of tunneling through ultra-thin gate dielectrics // J. Appl. Phys. 1997. Vol. 81, No 12. P. 7900–7908.

- Zhevnyak O. Temperature effect on electron transport in conventional short channel MOSFETs: Monte Carlo simulation // Proc. SPIE. 2008. Vol. 7025. P. 1M-1–8.